Un plan rempli automatiquement, c’est bien, mais enchainer les quatre automatiquement c’est encore mieux. En effet, lorsque l’on alimente la carte, la mémoire contient des données non initialisées, donnant un affichage erratique, qui n’est pas du plus beau cru. L’idéal serait de pouvoir remettre à zéro la mémoire vidéo automatiquement à l’allumage et par la suite pouvoir s’en servir pour réinitialiser la mémoire vidéo sur demande.

La méthode est la suivante, élaborer une machine d’état ‘MCHINIT’ qui vient piloter les actions successives provoquant le ‘vidage de la mémoire’.

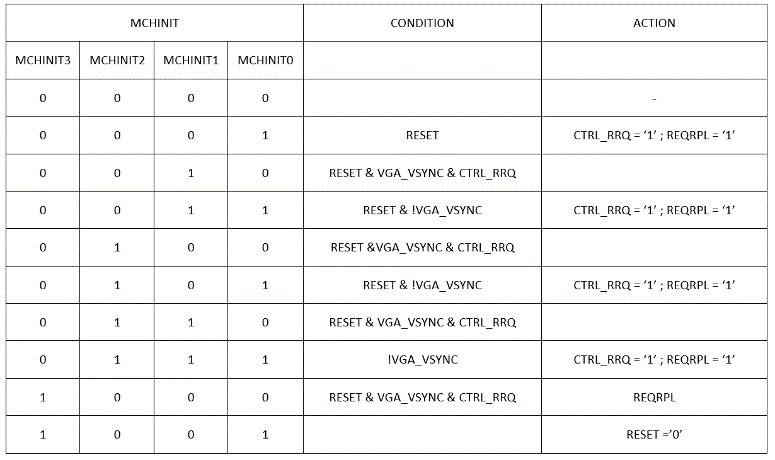

Pour déclencher un remplissage il suffit positionner CTRL_RRQ à ‘1’ à quatre reprises en ajustant la valeur des plans mémoire successivement à 0, 1, 2 ou 3. Les changements d’état de la machine sont décrits par la table de vérité :

On remarque que :

- Le Signal CTRL_RRQ passe à ‘1’ en même temps que MCHINIT0.

- La page sélectionnée CTRL_PL0 et CTRL_PL1 correspondent respectivement à MCHINIT1 et MCHINIT2.

- Ne disposant que d’une ligne d’horloge, il va falloir cumuler les conditions de passage d’un état à l’autre.

Ce qui donne:

CPLD ADRESSES

RESET.d = TRS_SYSRES; /* ATTENTE DE LA STABILISATION DU DEMARRAGE DU TRS-80 */

RESET.ck = MCL5;

RESET.ar = MCHINIT3 & MCHINIT1;

MCHINIT0.t = 'b'1; /* COMPTEUR SYNCHRONE DECRIVANT LES DIFFERENTES PHASES */

MCHINIT1.t = MCHINIT0;

MCHINIT2.t = MCHINIT1 & MCHINIT0;

MCHINIT3.t = MCHINIT2 & MCHINIT1 & MCHINIT0;

MCHINIT0.ck = RESET & !MCHINIT3 & !MCHINIT2 & !MCHINIT1 & !MCHINIT0 # RESET & (!MCHINIT0 & !VGA_VSYNC # MCHINIT0 & RPLACK & VGA_VSYNC );

MCHINIT1.ck = RESET & (!MCHINIT0 & !VGA_VSYNC # MCHINIT0 & RPLACK & VGA_VSYNC );

MCHINIT2.ck = RESET & (!MCHINIT0 & !VGA_VSYNC # MCHINIT0 & RPLACK & VGA_VSYNC );

MCHINIT3.ck = RESET & (!MCHINIT0 & !VGA_VSYNC # MCHINIT0 & RPLACK& VGA_VSYNC );

REQRPL = MCHINIT3 & !MCHINIT2 & !MCHINIT1 & !MCHINIT0;

CTRL_PL0.ap = RESET & MCHINIT1;

CTRL_PL0.ar = RESET & !MCHINIT1;

CTRL_PL1.ap = RESET & MCHINIT2;

CTRL_PL1.ar = RESET & !MCHINIT2;

CTRL_RRQ.ap = RESET & MCHINIT0;

L’état ‘1000’ est utilisé pour faire passer le signal REQRPL à ‘1’ en fin de process, cela permet de sur le CPLD Données de repositionner la sélection des plans couleur à 0 (CTRL_PL0 et CTRL_PL1).

CPLD DONNEES

CTRL_RRQ.ap = REQRPL;

CTRL_PL0.ar = REQRPL;

CTRL_PL1.ar = REQRPL;

A la fin du cycle complet (Etat ‘1001’) RESET passe à l’état ‘0’ Interdisant de nouveau changement d’état.

Pour le coup il est possible de déclencher manuellement un nouveau cycle en mettant à ‘0’ la machine à état.

CPLD ADRESSES

MCHINIT0.ar = TRS_A13 & MREQ & INOUT & !RDWR & !TRS_A0 & !TRS_A1;

MCHINIT1.ar = TRS_A13 & MREQ & INOUT & !RDWR & !TRS_A0 & !TRS_A1;

MCHINIT2.ar = TRS_A13 & MREQ & INOUT & !RDWR & !TRS_A0 & !TRS_A1;

MCHINIT3.ar = TRS_A13 & MREQ & INOUT & !RDWR & !TRS_A0 & !TRS_A1;