Les CPLD

Bien entendu, lors de la réalisation d'un projet en électronique, pour chaque fonction élémentaire ou bascule il faut intégrer un nouveau circuit électronique et la carte devient vite complexe et encombrante. Les circuits étant "câblés", elle est de même peu voir pas évolutive. A titre d’indication le TRS-80 modèle 1 est composé de cinquante cinq circuits logiques chacun composés de 1 à 8 fonctions logiques. Si l'on souhaite le faire évoluer et modifier son comportement, il faut couper des pistes ou créer des liaisons voire ajouter de nouveaux circuits, ce qui n’est très aisé.

Afin de simplifier et apporter plus de souplesse dans ce type de circuiterie, au fur et à mesure de l’évolution des technologies et notamment du degré d’intégration des fonctions dans les puces électroniques, ont été créés les réseaux logiques programmables. Il s'agit d'un ensemble limité à quelques entrées sorties, circuits logiques et bascules dont il est possible de programmer voire de reprogrammer les interconnexions.

Puis les CPLD sont apparus (Complexe Programmable Logic Device) intégrant beaucoup plus de ces composants élémentaires plusieurs centaines.

Enfin les FPGA (Field Programmable Gate Array) intégrant beaucoup plus de fonctionnalités complexes comme de la mémoire, des organes de calcul etc….

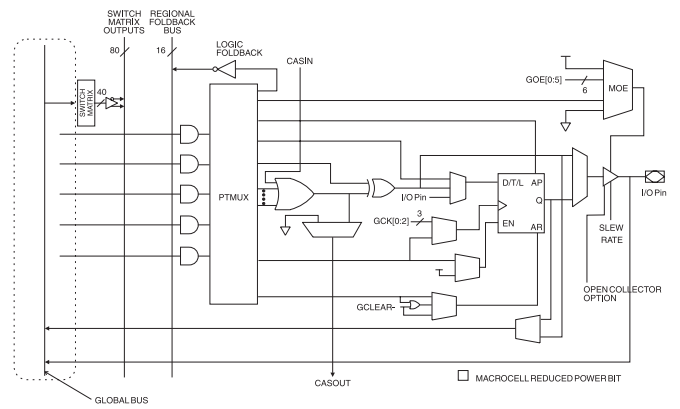

Dans le cadre de mes projets, pour différentes raisons exposées plus loin, nous allons considérer des CPLD dont voici à quoi ressemble une cellule de base.

Par exemple, les circuits que je vais utiliser par la suite disposent de 128 cellules identiques dont la moitié sont interconnectées avec les lignes externes. Les autre pouvant servir de registres internes. Dans chaque cellule, on retrouve une bascule est beaucoup de circuits logiques dont toutes les interconnexions sont programmables et reprogrammables de manière matricielle.

L’avantage est que le schéma électronique devient alors entièrement dynamique et reconfigurable.

On imagine bien qu’il est illusoire de chercher à positionner point à point chacune des interconnexions élémentaire. On se fait pour cela assister par une suite de logiciels qui permet le calcul, l'optimisation et l’intégration de ces points de raccordement à partir d'une description comportementale du circuit. Il suffit ainsi de décrire, par exemple, le circuit avec des équations booléennes, de les compiler puis téléverser dans les CPLD.

Pour l’exemple de tout à l’heure, la gestion de la lecture d’une mémoire deviendrait :

| CPLD |

|

|

Voilà, le tour est joué. Et si les conditions changent, il suffit de modifier l’équation, de recompiler et de téléverser la nouvelle version. Voici donc la technologie qui est utilisée dans ce projet.