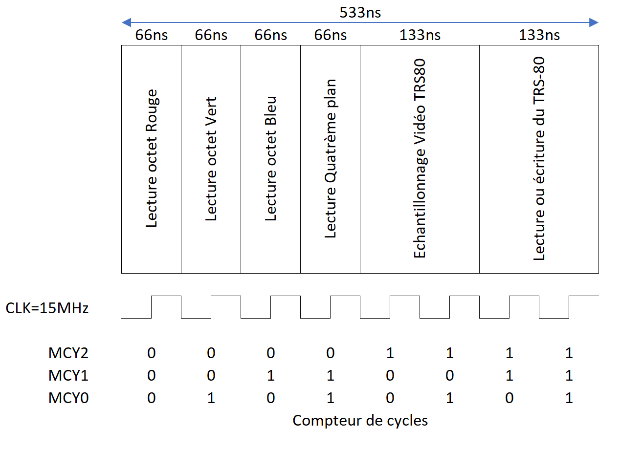

Si l’on reprend la séquence des cycles envisagée au début de l’étude, on voit que la lecture des pixels est réalisée dans la première partie du cycle, pour MCY2 = ‘0’.

On peut donc affirmer que pendant cette période, les signaux de la mémoire la forceront en lecture = ‘1’ et en sortie autorisée = ‘0’.

De la même façon le bus adresse sera composé des compteurs de colonnes suivis des compteurs de lignes.

CPLD ADRESSES

MEM_OE.t = !(MREQ & !INOUT & RDWR # !MCY2) ; /* ON AJOUTE LA NOUVELLE CONDITION DE LECTURE */

MEM_RW.d = !(MEMREQ & !INOUT & RDWR & MCY1 & !MCY0 # !MCY2) ;

MEM_ A0.d = TRS_A0 & MREQ & MCY2 & MCY1 # !MCY2 & MCL0 ; /* ADRESSAGE D’UNE LIGNE CARCTERE A CARACTERE */

…

MEM_ Ax = TRS_Ax & MREQ & MCY2 & MCY1 # !MCY2 & MCLx ;

…

MEM_ A5 = TRS_A5 & MREQ & MCY2 & MCY1 # !MCY2 & MCL5 ;

MEM_A0.ck = CLK ;

…

MEM_A5.ck = CLK ;

Les poids supérieurs vont maintenant correspondre aux lignes, à ceci près que nous devons doubler chaque ligne. Nous allons pour cela commencer par MLG1 plutôt que MLG0 ce qui permettra de lire deux fois la même ligne d’une trame horizontale à l’autre. En effet le numéro de ligne ne changera qu’au bout de la seconde lecture.

CPLD ADRESSES

/* ADRESSAGE DES LIGNES , ON DOUBLE LA LECTURE DE CHAQUE LIGNE */

MEM_ A6 = TRS_A6 & MREQ & MCY2 & MCY1 # !MCY2 & MLG1 ;

MEM_ A7 = TRS_A7 & MREQ & MCY2 & MCY1 # !MCY2 & MLG2 ;

MEM_ A8 = TRS_A8 & MREQ & MCY2 & MCY1 # !MCY2 & MLG3 ;

MEM_ A9 = TRS_A9 & MREQ & MCY2 & MCY1 # !MCY2 & MLG4 ;

MEM_ A10 = TRS_A10 & MREQ & MCY2 & MCY1 # !MCY2 & MLG5 ;

MEM_ A11 = TRS_A11 & MREQ & MCY2 & MCY1 # !MCY2 & MLG6 ;

MEM_ A12 = TRS_A12 & MREQ & MCY2 & MCY1 # !MCY2 & MLG7 ;

MEM_ A13 = TRS_A13 & MREQ & MCY2 & MCY1 # !MCY2 & MLG8 ; /* MLG8 – MLG1 PERMETTENT DE CODER LES 192 LIGNES */

MEM_ A14 = TRS_A14 & MREQ & MCY2 & MCY1 # !MCY2 & CTRL_PL0 ;

MEM_ A15 = TRS_A15 & MREQ & MCY2 & MCY1 # !MCY2 & CTRL_PL1 ;

MEM_A6.ck = CLK ;

…

MEM_A15.ck = CLK ;

Nous avons adressé un plan d’image soit 16ko, il faut s’occuper maintenant de la pagination. Les plans couleur dans un premier temps, puis les pages graphiques.

CPLD ADRESSES

NODE CTRL_PGL ;

MEM_ A16 = TRS_A16 & MREQ & MCY2 & MCY1 # !MCY2 & CTRL_PGL ;

Les adresses étant positionnées occupons nous des données.

Dans ce cycle il n’y a donc que de la lecture, il faut donc ne s’occuper que du BUS de données de la mémoire qui va être lue puis sérialisée vers la sortie VGA.

La lecture de l’octet rouge se fait dans le cycle MCY0, le vert à MCY1, le bleu à MCY2 et le quatrième plan à MCY3.

CPLD DONNEES

NODE [R7..0] ;

NODE [V7..0] ;

NODE [B7..0] ;

NODE [I7..0] ;

PIN = VGA_RG ;

PIN = VGA_VR ;

PIN_VGA_BL ;

R0.d = MEM_D0 & !MCY2 & !MCY1 & MCY0 ; /* MEMORISATION DU ROUGE A MCY-0 */

R1.d = MEM_D1 & !MCY2 & !MCY1 & MCY0 # R0 & (MCY2 # MCY1 # MCY0) ; /* MEMORISATION ET SERIALISATION */

…

Rx.d = MEM_Dx & !MCY2 & !MCY1 & MCY0 # Rx-1 & (MCY2 # MCY1 # MCY0) ;

…

R7.d = MEM_D7 & !MCY2 & !MCY1 & MCY0 # R6 & (MCY2 # MCY1 # MCY0) ;

V0.d = MEM_D0 & !MCY2 & !MCY1 & MCY0 ; /* MEMORISATION DU VERT A MCY-1 */

V1.d = MEM_D1 & !MCY2 & !MCY1 & MCY0 # V0 & (MCY2 # MCY1 # MCY0) ; /* MEMORISATION ET SERIALISATION */

…

Vx.d = MEM_Dx & !MCY2 & !MCY1 & MCY0 # Vx-1 & (MCY2 # MCY1 # MCY0) ;

…

V7.d = MEM_D7 & !MCY2 & !MCY1 & MCY0 # V6 & (MCY2 # MCY1 # MCY0) ;

B0.d = MEM_D0 & !MCY2 & MCY1 & !MCY0 ; /* MEMORISATION DU BLEU A MCY-2*/

B1.d = MEM_D1 & !MCY2 & MCY1 & !MCY0 # B0 & (MCY2 # MCY1 # MCY0) ; /* MEMORISATION ET SERIALISATION */

…

Bx.d = MEM_Dx & !MCY2 & MCY1 & !MCY0 # Bx-1 & (MCY2 # MCY1 # MCY0) ;

…

B7.d = MEM_D7 & !MCY2 & MCY1 & !MCY0 # B6 & (MCY2 # MCY1 # MCY0) ;

I0.d = MEM_D0 & !MCY2 & MCY1 & MCY0 ; /* MEMORISATION DU 4E PLAN A MCY-3 */

I1.d = MEM_D1 & !MCY2 & MCY1 & MCY0 # I1 & (MCY2 # MCY1 # MCY0) ; /* MEMORISATION ET SERIALISATION */

…

Ix.d = MEM_Dx & !MCY2 & MCY1 & MCY0 # Ix & (MCY2 # MCY1 # MCY0) ;

…

I7.d = MEM_D7 & !MCY2 & MCY1 & MCY0 # I7 & (MCY2 # MCY1 # MCY0) ;

Rx.ck = !CLK ; /* SYNCHRO AU CHANGEMENT D’ETAT DE MCY */

Vx.ck = !CLK ;

Bx.ck = !CLK ;

Ix.ck = !CLK ;

VGA_RG = B7; /* AFFICHAGE DES COMPOSANTES R, V ET B */

VGA.VR = V7 ;

VGA.BL = B7 ;

VGA_RG.ck = CLK ;

VGA_VR.ck = CLK ;

VGA_BL.ck = CLK ;

Nous avons affiché les composantes rouge, verte et bleue, pour le quatrième plan, c’est un peu différent car elle utilise les mêmes couleurs et peut se positionner devant ou derrière le graphique pour la vidéo native du TRS-80. Il peut également servir de demi-teinte.

La vidéo native s’affiche pour tout bit de la page n°4 valant ‘1’, si elle est sélectionnée (CTLA_VT = ‘1’) si elle s’affiche devant les graphismes (CTLA_DV = ‘1’), dans le cas où elle est positionnée derrière les graphismes (CTLA_DV = ‘0’) si aucun graphique n’est affiché (R7 = ‘0’ et V7 = ‘0’ et B7 = ‘0’) sinon c’est ce sont les couleurs graphiques R7, V7 et B7 qui s’affichent.

Soit l’équation suivante :

VGA_RG = CTLA_VT & (R7 # CLTLA_DV & (I7 # !I7 & R7) # !CTLA_DV & !R7 & !V7 & !B7 & I7)

Ce qui nous donne :

CPLD DONNEES

VGA_RG = CTLA_VT & (R7 # CTLA_DV & (I7 # !I7 & R7) # !CTLA_DV & !R7 & !V7 & !B7 & I7) ;

VGA_VR = CTLA_VT & (V7 # CTLA_DV & (I7 # !I7 & V7) # !CTLA_DV & !R7 & !V7 & !B7 & I7) ;

VGA_BL = CTLA_VT & (B7 # CTLA_DV & (I7 # !I7 & B7) # !CTLA_DV & !R7 & !V7 & !B7 & I7) ;

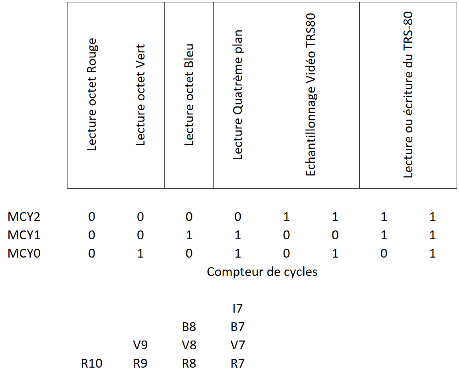

En fait cela n’est pas satisfaisant car on dispose de I7 à MCY-4, donc B7 a été décalé, V7 décalé deux fois et R7 trois fois. C’est inhérent au fait que les octets des plans sont lus avec le décalage d’un cycle.

En fait cela n’est pas satisfaisant car on dispose de I7 à MCY-4, donc B7 a été décalé, V7 décalé deux fois et R7 trois fois. C’est inhérent au fait que les octets des plans sont lus avec le décalage d’un cycle.

Pour que tous les bits soient en phase, il est nécessaire de disposer des registres à décalages plus grand, car il nous faut retarder les couleurs Rouge, Verte et Bleue d’autant de cycles.

CPLD DONNEES

NODE [R10..0] ;

NODE [V9..0] ;

NODE [B8..0] ;

R8.d = R7 ;

R9.d = R8 ;

R10.d = R9 ;

R8.ck = !CLK ;

R9.ck = !CLK ;

R10.ck = !CLK ;

V8.d = V7 ;

V9.d = V8 ;

V8.ck = !CLK ;

V9.ck = !CLK ;

B8.d = B7 ;

B8.ck = !CLK ;

VGA_RG = CTLA_DV & (R10 # CLTLA_DV & (I7 # !I7 & R10) # !CTLA_VT & !R10 & !V9 & !B8 & I7) ;

VGA_VR = CTLA_DV & (V9 # CLTLA_DV & (I7 # !I7 & V9) # !CTLA_VT & !R10 & !V9 & !B8 & I7) ;

VGA_BL = CTLA_DV & (B8 # CLTLA_DV & (I7 # !I7 & B8) # !CTLA_VT & !R10 & !V9 & !B8 & I7) ;

La vidéo est bien calée, alors c’est fini ?

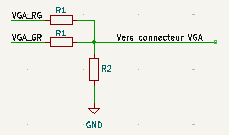

Et bé non, il reste à gérer les demi-teintes et pour cela on va se servir d’une sortie supplémentaire qui va modifier le niveau électrique des sorties VGA selon le schéma suivant :

Les tensions ramenées par les deux signaux VGA_xx sont identiques les résistances connectées sur ces lignes seront donc identiques.

La tension de sortie doit être de 0.7V chargées sur une impédance de 75Ω, on considèrera donc une tension à vide 1.4V avec une impédance de sortie de 75 Ω.

Il vient donc ${\displaystyle R_{S} = \frac{\frac{R_{1}}{2}.R_{2}}{\frac{R_{1}}{2}+R_{2}} = 75 \Omega}$

Calculons, d’autre part, la valeur de la tension de sortie pour VGA_RG = ’1’, celle-ci doit contribuer à la moitié de la tension escomptée (théorème de superposition) :

${\displaystyle \frac{\frac{R_{1}.R_{2}}{R_{1} + R_{2}}}{\frac{R_{1}.R_{2}}{R_{1}.R_{2}}+R_{1}} = \frac{0,7V}{5V} \Leftrightarrow R_{1}.R_{2} = 0,14.R_{1}.R_{2} + 0,14.R_{1}.(R_{1} + R_{2}) \Leftrightarrow 1 = 0,14 + 0,14.\frac{R_{1} + R_{2}}{R_{2}} \Leftrightarrow \frac{0,86}{0,14} = \frac{R_{1} + R_{2}}{R_{2}} = \frac{2,57.R_{2}^2}{3,57.R_{2}} = 0,72.R_{2} = 75 }$

donc ${R_{2} = \frac{75}{0,72} = 104 \Omega}$ et finalement ${\displaystyle R_{1} = 5,14.R_{2} = 535 \Omega}$. Nous choisirons les valeurs normalisées 100Ω et 560Ω

Ce qui nous donne une impédance de 73,7Ω et, si VGA_GR = '0', une tension de sortie pour VGA_RG de 0,132 x 5 = 0,66 V, ce qui est proche du résultat attendu de 0,7V sur 75Ω.

CPLD DONNEES

PIN = VGA_GR ;

PIN = VGA_GV ;

PIN = VGA_GB ;

VGA_GR = VGA_RG & !CTRL_DT # I7 & CTRL_DT; /* RECOPIE VGA_RG SI COULEUR PLEINE SINON PREND LA VALEUR I7 */

VGA_GV = VGA_VR & !CTRL_DT # I7 & CTRL_DT;

VGA_GB = VGA_BL & !CTRL_DT # I7 & CTRL_DT;