Ce paragraphe nécessite au préalable une connaissance dans la logique booléenne et des fonctions logiques de base.

Ce paragraphe nécessite au préalable une connaissance dans la logique booléenne et des fonctions logiques de base.

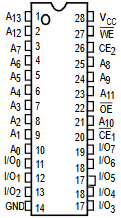

Afin de fonctionner une mémoire a, par exemple, besoin de savoir que l’on s’adresse à elle ? Elle est donc sélectionnée comme périphérique adressé à l'aide du signal CS.

Les données sont échangées sur le bus de données (I/O0 à I/O7 pour cette mémoire D0 à D7 pour le processeur) en fonction du sens de transfert indiqué par la ligne WE (Write Enable). L'adresse de destination ou de provenance des données est précisée par le processeur sur le bus d’adresse, ici A0 à A13 soit 16ko.

Un signal supplémentaire permet de gérer l’activation du bus de données en sortie, dans le cas d'une lecture de la mémoire. Il s’agit du signal OE (Output Enable), qui permet au processeur de n’autoriser qu’un seul périphérique pour dialoguer sur le bus et donc prévenir les collisions potentielles.

L’art du combinatoire

Si l’on revient sur l'exemple du cycle de lecture du chronogramme précédent, on remarque qu’il est nécessaire de détecter plusieurs conditions pour générer ces signaux.

En effet, une requête de lecture demande à ce que les signaux CE1 et CE2 soient valides en même temps, donc à ‘0’ logique. WE signale le sens du transfert.

D’autre part, la mémoire physique doit être sélectionnée pour une fenêtre d’adresse, en effet le processeur peut adresser jusqu'à 64ko, et notre exemple ne comporte que 16ko qui peuvent être positionner n’importe où dans l’espace d’adressage. Il faut donc être en mesure de décoder le bus d'adresse du processeur afin savoir s’il s’adresse bien à notre mémoire et non pas à un autre périphérique.

Nous allons considérer que notre mémoire est positionnée dans la fenêtre ${$}$C000 à ${$}$FFFF, soit si l’on décomposer en binaire le bus d’adresse :

| A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | |

| $C000 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| --- | 1 | 1 | x | x | x | x | x | x | x | x | x | x | x | x | x | x |

| $FFFF | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

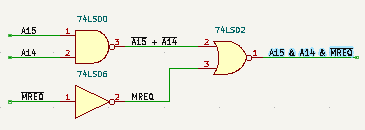

On peut constater que toutes les adresses correspondant à la mémoire possèdent leurs poids A15 et A14 positionnés à ‘1’. Le signal de sélection de la mémoire "CE" (Chip Enable) est donc valide si A15 = ‘1’, A14 = ‘1’ et MREQ = ‘0’ (MREQ actif à ‘0’).

Le signal WE actif à zéro doit être l’opposé du signal RD du processeur. Enfin le bus de données étant rendu disponible par le processeur lors du cycle de lecture, on peut valider la sortie des données de la mémoire sur ce bus OE lorsque MREQ est valide puisque la lecture des données est effectuée avant qu’il soit désactivé (qu’il repasse à ‘1’).

Dans notre cas, on fixera le signal CE1 à ‘0’ et pour le signal CE2 correspondra à notre CE. Nous pourrions obtenir le schéma ci-après avec l’utilisation de circuits électroniques.

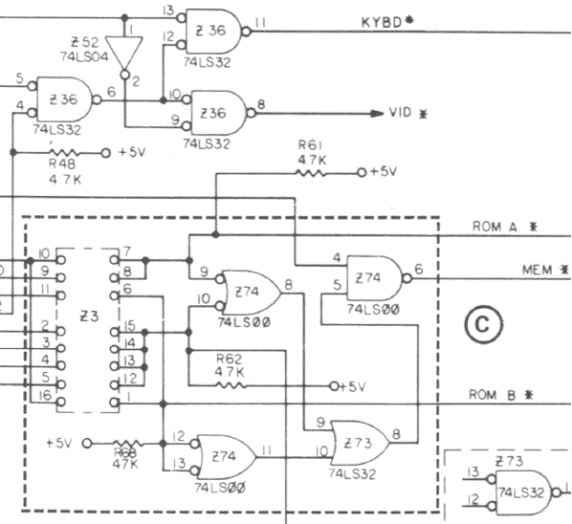

Il faut pour cela être familier de l’algèbre de Bool et de l’utilisation des fonctions logiques. Comme on peut en voir sur l’extrait de schéma ci-contre, c’est de de cette manière qu’opère le TRS-80 pour la gestion de l’adressage de la mémoire vidéo, du clavier, de la ROM ou de la RAM.